### **Product Brief**

Intel® vRAN Dedicated Accelerator ACC100

# Unleash the Speed of 4G and 5G Virtualized Radio Access Networks (vRAN)

## Higher capacity 4G/LTE and 5G vRANs cells/carriers with the Intel® vRAN Dedicated Accelerator ACC100

#### **5G Edge-Based Services**

As communications service providers move from 4G to 5G networks, many are adopting virtualized radio access network (vRAN) architecture for higher channel capacity and easier deployment of edge-based services and applications. vRAN solutions are ideally located to deliver low-latency services with the flexibility to increase or decrease capacity based on the volume of real-time traffic and demand on the network.

## 4G and 5G Forward Error Correction (FEC) Acceleration

One of the most compute-intensive 4G and 5G workloads is RAN layer 1 (L1) forward error correction (FEC), which resolves data transmission errors over unreliable or noisy communication channels. FEC technology detects and corrects a limited number of errors in 4G or 5G data without the need for retransmission. FEC is a very common function that is not differentiated across vendor implementations. Since the FEC acceleration transaction does not contain cell state information, it can be easily virtualized, enabling pooling benefits and easy cell migration.

#### **Increased vRAN Cell Density and Efficiency**

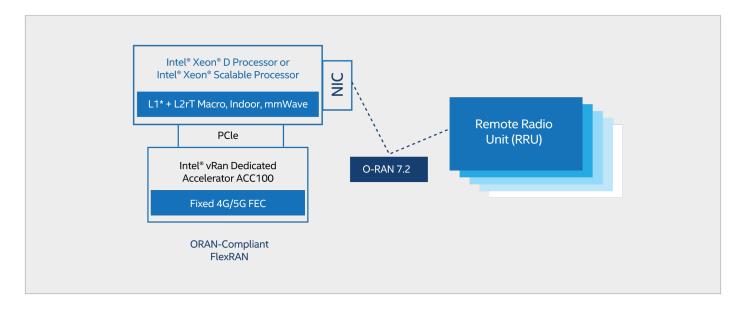

The Intel® vRAN Dedicated Accelerator ACC100 rapidly performs Layer 1 FEC algorithms, making more processing power available for increased channel capacity on edgebased services and applications. The accelerator is a dedicated device that works with Intel® Xeon® Scalable processors and Intel® Xeon® D processors to enable low-cost, power-efficient 4G and 5G vRAN solutions. The accelerator card connects to the server processor via a standard PCIe Gen 3 x16 interface.

#### **Fast Time-to-Market**

The ACC100 supports the O-RAN adopted DPDK BBDev API an API which Intel contributed to the opensource community to enable choice and TTM for FEC acceleration solutions. The FlexRAN software reference architecture supports the ACC100 which enables users to quickly evaluate and build platforms for the wide range of vRAN networks.

| Intel® vRAN Dedicated Accelerator ACC100 |                                                                                                                                                       |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main Benefits                            | Reduces platform power, E2E latency and Intel® CPU core count requirements as well as increases cell capacity than existing programmable accelerator  |

|                                          | Accelerates both 4G and 5G data concurrently                                                                                                          |

|                                          | Lowers development cost using commercial off the shelf (COTS) servers                                                                                 |

|                                          | Accommodates space-constrained implementations via a low-profile PCIe card form factor.                                                               |

|                                          | Enables a variety of flexible FlexRAN deployments from small cell to macro to Massive<br>MIMO networks                                                |

|                                          | Supports extended temperature for the most challenging of RAN deployment scenario's                                                                   |

| Hardware Features                        | LDPC FEC processing for 3GPP 5G:  • LDPC encoder/decoder  • Code block CRC generation/checking  • Rate matching/de-matching  • HARQ buffer management |

|                                          | Turbo FEC processing for 3GPP 4G:  • Turbo encoder/decoder  • Code block CRC generation/checking  • Rate matching/de-matching                         |

|                                          | Scalable to required system configuration                                                                                                             |

|                                          | Hardware DMA support                                                                                                                                  |

|                                          | Performance monitoring                                                                                                                                |

|                                          | Load balancing supported by the hardware queue manager (QMGR)                                                                                         |

| Software and Cloud<br>Support            | Interface through the DPDK BBDev library and APIs     Linux OS supported                                                                              |

$Intel\,technologies\,may\,require\,enabled\,hardware, software\,or\,service\,activation.$

No product or component can be absolutely secure.

Your costs and results may vary.

Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Other names and brands may be claimed as the property of others.

© 2020 Intel Corporation Printed in USA 0928/FS/ICMCSW/PDF 🗳 Please Recycle 344766-001 US