# WHITE PAPER

Communications Service Providers Open Source NFV Scalability

# Scalability of Enea NFV Core\* Shown Using Intel® Processors

Enea NFV Core is designed to deliver virtualized services on between 2 and 100 servers; tests on Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Gold processor-based servers show scalable performance as number of cores and flows are increased.<sup>1</sup>

# ENEA

# The Challenge: Making Open Source NFV Suitable for CommSPs

Open source NFV such as OpenStack,\* Open Platform for Network Functions Virtualization (OPNFV),\* Open Networking Automation Platform (ONAP),\* and others are an increasingly popular alternative for communications service providers (CommSPs) that are virtualizing their networks. Open source solutions are community developed, which brings innovation and a fast response to bugs or security breaches. This makes open source software well suited to CommSPs that are building out new networks optimized for service provisioning agility and service innovation.

But open source NFV software is designed to serve the needs of the entire community, which means that CommSPs must secure the software and integrate other open source software components to meet the needs of high-availability and high-performance CommSP networks.

Even with all of the benefits to be gained from open source NFV software, CommSPs are concerned about software stability, security, interoperability, and performance. Many CommSPs are embracing DevOps organizations to make open source NFV services operational, but they also are looking for hardened NFV software as a starting point.

To fill this need, Intel<sup>®</sup> Network Builders ecosystem partner Enea has developed Enea NFV Core, a virtualization platform built using OPNFV and OpenStack, with performance, availability, functionality, and scalability enhancements for CommSP networks. Enea NFV Core is designed for applications including multi-access edge computing (MEC), 5G and virtual customer premises equipment (vCPE), CommSP data centers, central office (CO), and edge points of presence (PoPs).

To be cost effective in all of these use cases, Enea NFV Core must offer scalable performance across a range of server configurations. This white paper describes Enea NFV Core and presents the results of testing by Enea to demonstrate performance scalability.

# **Enea NFV Core**

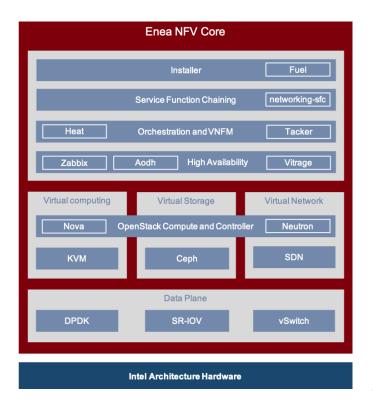

Enea NFV Core is an NFV platform that combines virtualized compute, network, storage, and management and operations (MANO). The software builds on OpenStack and OPNFV with carrier network functionality added through the integration of open source software including Data Plane Development Kit (DPDK), Open vSwitch (OvS), Vitrage, Zabbix, Tacker, Aodh, Ceph, and others (see sidebar and Figure 1).\* The company is an OPNFV leading contributor and has worked with the group to verify the interoperability of the software.

### **Table of Contents**

| The Challenge1                               |

|----------------------------------------------|

| Enea NFV Core 1                              |

| Testing the Scalability<br>of Enea NFV Core2 |

| Five Test Scenarios 2                        |

| Conclusion5                                  |

| About Enea5                                  |

| About Intel® Network Builders 5              |

In addition to this integration, Enea's engineering team has spent hundreds of hours tuning the parameters of the software to support CommSP use cases. These optimizations are designed to allow the software to serve as the NFV solution for virtualized services.

Figure 1. Block diagram of Enea NFV Core.<sup>1</sup>

# **Testing the Scalability of Enea NFV Core**

Enea NFV Core is designed to be able to efficiently scale with the number of CPU resources and the number of data flows. Enea devised the following series of performance tests to demonstrate that performance scalability in an environment that represents a typical NFV use case featuring north-south data flows.

For the tests, Enea chose servers powered by the Intel® Xeon® Scalable Gold 6152 processor. The 22-core Intel Xeon Gold 6152 operates at a base frequency of 2.1 GHz and is part of the Intel Xeon Scalable platform, Intel's latest CPUs for virtualized, cloud-optimized network applications. In addition to the open source DPDK features, Enea also leveraged Intel® Advanced Vector Extensions 512 (Intel® AVX-512), which delivers workload-optimized performance and throughput increases for data compression workloads.

Using the PROX traffic generator and testpmd for packet forwarding, Enea set up a north-south the data flow between the PHY server on one side, and the VM, which runs on the Enea NFV Core server and is connected through OVS, on the other side. To show scalability, the number of cores dedicated to the OVS was increased and the resulting change in the packet throughput was logged. The results were measured with the constraint of almost zero packet

# **Enea NFV Core Key Components**

- OpenStack core services include Horizon, Nova, Neutron, Cinder, Glance, Swift, Keystone, Congress, Heat, Tacker and Ceilometer.\*

- Compute node software package that includes Linux\* OS, KVM,\* and DPDK packet throughput acceleration.

- Service function chaining (SFC) that is enabled through standardized networking APIs.

- Extended fault management baseline with an open source telco-grade high availability solution to meet CommSP availability requirements.

- Supports orchestration via OpenStack Heat Templates (HOT)\* and features integrated OpenStack Tacker\* as a lightweight orchestrator and TOSCA parser.

- OpenDaylight\* Oxygen\* is available as software defined networking (SDN) controller on request.

loss for throughput per RFC2544. With these side-by-side configurations, Enea demonstrates how performance can be customized to meet the workloads involved in a variety of use cases, ranging from customer premises server to edge of the network applications, or even in the network core.

### **Five Test Scenarios**

Servers featuring Intel Xeon Scalable Gold 6152 CPUs were used as the hardware platform for the tests. Each server configuration featured two 40 Gbps Ethernet NICs with both ports in use for the tests. Enea varied both the number of data flows per port and the number of CPU cores assigned to the OVS to show throughput at different resource levels. Specific flow and server configuration scenarios utilized in the tests included:

- Scenario 1: 1 flow per port with 1 core assigned to OVS

- Scenario 2: 1 flow per port with 2 cores assigned to OVS

- Scenario 3: 1 flow per port with 4 cores assigned to OVS

- Scenario 4: 2 flows per port with 4 cores assigned to OVS

- Scenario 5: 4 flows per port with 8 cores assigned to OVS

The results of the tests using Scenario 1 and Scenario 2 configurations are shown in Tables 1 and 2.<sup>2</sup> The tables show that throughput performance of Enea NFV Core is very consistent and scales linearly with additional processing resources assigned to OVS for small packet sizes (64 bytes up to 256 bytes). The results show nearly linear scalability for packets bigger than 512 bytes. Both the TX and RX measurements in the columns below were made on the PHY for each port on the PROX side. The TX and RX percentages represent the percentage of total available throughput (2 x 40 Gbps NICs) consumed by the data flows.

|      | THROUGHPUT            |                       |                         |                      |                         |                      |  |  |

|------|-----------------------|-----------------------|-------------------------|----------------------|-------------------------|----------------------|--|--|

|      | RX (KPPS PER<br>PORT) | TX (KPPS PER<br>PORT) | RX (MBPS PER<br>SERVER) | RX (% PER<br>SERVER) | TX (MBPS PER<br>SERVER) | TX (% PER<br>SERVER) |  |  |

| 6.4  | 1525                  | 1530                  | 2040.0                  | 2.6                  | 2056.3                  | 2.6                  |  |  |

| 64   | 1525                  | 1530                  | 2049.6                  |                      |                         |                      |  |  |

| 128  | 1448                  | 1451                  | 3428.8                  | 4.2                  | 3435.9                  | 4.2                  |  |  |

| 128  | 1448                  | 1451                  |                         |                      |                         |                      |  |  |

| 250  | 1358                  | 1360                  | 5996.9                  | 7.4                  | 6005.7                  | 7.5                  |  |  |

| 256  | 1358                  | 1360                  |                         |                      |                         |                      |  |  |

| 540  | 1265                  | 1271                  | 10767.6                 | 13.4                 | 10818.7                 | 13.5                 |  |  |

| 512  | 1265                  | 1271                  |                         |                      |                         |                      |  |  |

| 1024 | 951                   | 951                   | 15885.5                 | 19.8                 | 15885.5                 | 19.8                 |  |  |

|      | 951                   | 951                   |                         |                      |                         |                      |  |  |

PHY-VM-PHY - 2 PORTS, 1 OVS CORE, 1 FLOW PER PORT

#### Table 1. Test results from Scenario 1.<sup>2</sup>

#### PHY-VM-PHY - 2 PORTS, 2 OVS CORES, 1 FLOW PER PORT

| THROUGHPUT  |                       |                       |                         |                      |                         |                      |  |

|-------------|-----------------------|-----------------------|-------------------------|----------------------|-------------------------|----------------------|--|

|             | RX (KPPS PER<br>PORT) | TX (KPPS PER<br>PORT) | RX (MBPS PER<br>SERVER) | RX (% PER<br>SERVER) | TX (MBPS PER<br>SERVER) | TX (% PER<br>SERVER) |  |

| 64          | 3099                  | 3099                  |                         | 5.2                  | 4165.1                  | 5.2                  |  |

| 64          | 3098                  | 3099                  | 4164.3                  |                      |                         |                      |  |

| 120         | 2892                  | 2900                  | 6848.2                  | 8.5                  | 6867.2                  | 8.5                  |  |

| 128         | 2892                  | 2900                  |                         |                      |                         |                      |  |

| 250         | 2629                  | 2630                  | 11609.6                 | 14.5                 | 11614.1                 | 14.5                 |  |

| 256         | 2629                  | 2630                  |                         |                      |                         |                      |  |

| <b>E</b> 40 | 2225                  | 2230                  | 18939.2                 | 23.6                 | 18981.7                 | 23.7                 |  |

| 512         | 2225                  | 2230                  |                         |                      |                         |                      |  |

| 1024        | 1503                  | 1510                  | 25106.1                 | 31.3                 | 25223.0                 | 31.5                 |  |

|             | 1503                  | 1510                  |                         |                      |                         |                      |  |

#### Table 2. Test results from Scenario 2.<sup>2</sup>

This scalability effect holds true when the number of cores is increased to four as in the scenarios shown in Tables 3 and 4. But Table 4 also shows the impact of increasing the number of flows to two per port. Throughput in Scenario 4 compared to Scenario 3 shows small-packet size performance improvement of approximately 14 percent, while the larger packet sizes demonstrate a larger performance increase of just under 26 percent.<sup>2</sup> As expected, larger-packet throughput should have a larger performance increase because of the reduced number of packets that need to be processed at larger packet sizes.

#### PHY-VM-PHY - 2 PORTS, 4 OVS CORES, 1 FLOW PER PORT

|    | THROUGHPUT            |                       |                         |                      |                         |                      |  |

|----|-----------------------|-----------------------|-------------------------|----------------------|-------------------------|----------------------|--|

|    | RX (KPPS PER<br>PORT) | TX (KPPS PER<br>PORT) | RX (MBPS PER<br>SERVER) | RX (% PER<br>SERVER) | TX (MBPS PER<br>SERVER) | TX (% PER<br>SERVER) |  |

| 64 | 5279                  | 5500                  | 7004.2                  | 8.8                  | 7392.6                  | 9.2                  |  |

| 64 | 5278                  | 5501                  | 7094.3                  |                      |                         |                      |  |

| 128  | 4850 | 4866 | 11485.9 | 14.3 | 11522.6 | 14.4 |

|------|------|------|---------|------|---------|------|

|      | 4851 | 4866 |         |      |         |      |

| 256  | 4460 | 4492 | 19693.1 | 24.6 | 19838.8 | 24.7 |

| 256  | 4459 | 4493 |         |      |         |      |

| 512  | 4042 | 4100 | 34575.7 | 43.2 | 34899.2 | 43.6 |

|      | 4082 | 4100 |         |      |         |      |

| 1024 | 2428 | 2450 | 407227  | 50.9 | 40924.8 | 51.1 |

|      | 2449 | 2450 | 40732.7 |      |         |      |

### Table 3. Test results from Scenario 3.<sup>2</sup>

#### PHY-VM-PHY - 2 PORTS, 4 OVS CORES, 2 FLOWS PER PORT

| THROUGHPUT |                       |                       |                         |                      |                         |                      |  |

|------------|-----------------------|-----------------------|-------------------------|----------------------|-------------------------|----------------------|--|

|            | RX (KPPS PER<br>PORT) | TX (KPPS PER<br>PORT) | RX (MBPS PER<br>SERVER) | RX (% PER<br>SERVER) | TX (MBPS PER<br>SERVER) | TX (% PER<br>SERVER) |  |

| 64         | 5968                  | 5979                  | 0006.0                  | 10.0                 | 8032.4                  | 10.0                 |  |

| 64         | 5946                  | 5974                  | 8006.2                  |                      |                         |                      |  |

| 128        | 5531                  | 5540                  | 120405                  | 16.3                 | 13118.7                 | 16.3                 |  |

| 128        | 5483                  | 5540                  | 13040.5                 |                      |                         |                      |  |

| 256        | 4898                  | 4899                  | 21569.9                 | 26.9                 | 21636.1                 | 27.0                 |  |

| 250        | 4871                  | 4900                  |                         |                      |                         |                      |  |

| F12        | 4140                  | 4143                  | 35175.8                 | 43.9                 | 35265.2                 | 44.1                 |  |

| 512        | 4125                  | 4143                  |                         |                      |                         |                      |  |

| 1024       | 3048                  | 3049                  | 50620.1                 | 63.2                 | 50930.4                 | 63.6                 |  |

|            | 3015                  | 3049                  | 50638.1                 |                      |                         |                      |  |

#### Table 4. Test results from Scenario 4.<sup>2</sup>

Finally, Table 5 shows Enea NFV Core being able to process a large number of packets even with a single VNF. In this configuration, one VNF can process up to 90 percent of the 80 Gbps maximum throughput (for large packets) of the dual 40 Gbps NIC installed on the Intel Xeon Gold processor-based server.<sup>2</sup>

| PHY-VM-PHY - 2 PORTS, 8 OVS CORES, 4 FLOWS/PORT |                       |                       |                         |                      |                         |                      |  |  |

|-------------------------------------------------|-----------------------|-----------------------|-------------------------|----------------------|-------------------------|----------------------|--|--|

| THROUGHPUT                                      |                       |                       |                         |                      |                         |                      |  |  |

|                                                 | RX (KPPS PER<br>PORT) | TX (KPPS PER<br>PORT) | RX (MBPS PER<br>SERVER) | RX (% PER<br>SERVER) | TX (MBPS PER<br>SERVER) | TX (% PER<br>SERVER) |  |  |

| 64                                              | 10458                 | 10493                 | 14075.0                 | 17.5                 | 14103.2                 | 17.6                 |  |  |

| 64                                              | 10487                 | 10494                 | 14075.0                 |                      |                         |                      |  |  |

| 120                                             | 9572                  | 9578                  | 22590.7                 | 28.2                 | 22680.7                 | 28.3                 |  |  |

| 128                                             | 9508                  | 9578                  |                         |                      |                         |                      |  |  |

| 256                                             | 8551                  | 8559                  | 37639.7                 | 47.0                 | 37798.7                 | 47.2                 |  |  |

| 256                                             | 8496                  | 8560                  |                         |                      |                         |                      |  |  |

| 540                                             | 6426                  | 6432                  | 54544.8                 | 68.1                 | 54753.4                 | 68.4                 |  |  |

| 512                                             | 6390                  | 6433                  |                         |                      |                         |                      |  |  |

| 1024                                            | 4325                  | 4328                  | 72269.8                 | 00.2                 | 72294.9                 | 00.3                 |  |  |

| 1024                                            | 4328                  | 4328                  |                         | 90.3                 |                         | 90.3                 |  |  |

## Conclusion

The success of virtualization in CommSP networks starts with an NFV platform that is customized for the unique needs of those networks. This includes DPDK for high performance, orchestration, service function chaining, fault management, and other functionality. Enea NFV Core's software features this functionality along with scalable performance for use cases at the edge and at the core of the network. The company has shown this scalable performance in tests utilizing Intel Xeon Scalable Gold 6152 processor-based servers. Enea NFV Core brings the benefits of open source NFV to CommSP networks with the performance and features required to meet their specialized needs.

# **About Enea**

Enea develops the software foundation for the connected society. We supply NFVI software platforms, embedded DPI, real-time operating systems, video traffic management, cloud data management, and professional services. Solution vendors, Systems Integrators, and Service Providers use Enea to create new networking products and services faster, better and at a lower cost. More than 3 billion people around the globe already rely on Enea technologies in their daily lives. Enea is listed on Nasdaq Stockholm. For more information: www.enea.com.

# **About Intel® Network Builders**

Intel Network Builders is an ecosystem of infrastructure, software, and technology vendors coming together with communications service providers and end users to accelerate the adoption of solutions based on network functions virtualization (NFV) and software defined networking (SDN) in telecommunications and data center networks. The program offers technical support, matchmaking, and co-marketing opportunities to help facilitate joint collaboration through to the trial and deployment of NFV and SDN solutions. Learn more at http://networkbuilders.intel.com.

<sup>1</sup> Figure provided courtesy of Enea. Other names and brands may be claimed as the property of others.

<sup>2</sup> Tests conducted by Enea. Configurations: servers powered by 2.1 GHz, 22-core Intel<sup>®</sup> Xeon<sup>®</sup> Gold 6152 processors with 188 GB of RAM. The servers featured two 40 Gbps NICs. Software included Enea NFV Core 1.1 release with DPDK 17.11 (host) and DPDK 18.05 (VM). PROX was used to generate packets and testpmd was used for packet forwarding.

Software and workloads used in performance tests may have been optimized for performance only on Intel microprocessors.

Performance tests, such as SYSmark and MobileMark, are measured using specific computer systems, components, software, operations and functions. Any change to any of those factors may cause the results to vary. You should consult other information and performance tests to assist you in fully evaluating your contemplated purchases, including the performance of that product when combined with other products. For more complete information visit www.intel.com/benchmarks.

Performance results are based on testing as of Nov. 23, 2018, and may not reflect all publicly available security updates. See configuration disclosure for details. No product or component can be absolutely secure.

Intel does not control or audit third-party data. You should review this content, consult other sources, and confirm whether referenced data are accurate.

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No product or component can be absolutely secure. Check with your system manufacturer or retailer or learn more at intel.com.

Optimization Notice: Intel's compilers may or may not optimize to the same degree for non-Intel microprocessors for optimizations that are not unique to Intel microprocessors. These optimizations include SSE2, SSE3, and SSSE3 instruction sets and other optimizations. Intel does not guarantee the availability, functionality, or effectiveness of any optimization on microprocessors not manufactured by Intel. Microprocessor-dependent optimizations in this product are intended for use with Intel microprocessors. Certain optimizations not specific to Intel microarchitecture are reserved for Intel microprocessors. Please refer to the applicable product User and Reference Guides for more information regarding the specific instruction sets covered by this notice.

#### Notice Revision #20110804

© Intel Corporation. Intel, the Intel logo, and Xeon are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others. 0319/DO/H09/PDF 🖧 Please Recycle 338843-001US

5